# Costruzione di una CPU dimostrativa

| Versione A: caricamento ed esecuzione del codice                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 81/                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Versione B: indice della memoria                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 831                                                                                                                                          |

| Istruzioni «load»                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 833                                                                                                                                          |

| Istruzioni «store»                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 833                                                                                                                                          |

| Versione C: registri generici                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 837                                                                                                                                          |

| Versione D: ALU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                              |

| Istruzione «not»                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | .846                                                                                                                                         |

| Istruzione «and»                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                              |

| Istruzione «or»                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                              |

| Istruzione «xor»                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 848                                                                                                                                          |

| Istruzioni «lshl» e «lshr»                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 849                                                                                                                                        |

| Istruzioni «ashl» e «ashr»                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |

| Istruzioni «rotl» e «rotr»                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |

| Istruzione «add»                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                              |

| Istruzione «sub»                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                              |

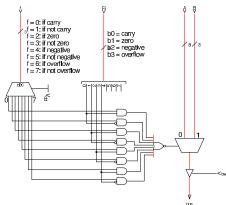

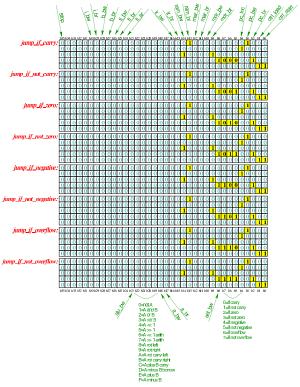

| Versione E: indicatori                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                              |

| Istruzione «rotcl» e «rotcr»                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | .857                                                                                                                                         |

| Istruzione «add_carry»                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                              |

| Istruzione «sub_borrow»                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .860                                                                                                                                         |

| Versione F: condizioni                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 863                                                                                                                                          |

| Versione G: pila                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 869                                                                                                                                          |

| Istruzioni «push» e «pop»                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | .873                                                                                                                                         |

| Istruzioni «call» e «return»                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | .873                                                                                                                                         |

| Versione H: I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 875                                                                                                                                          |

| Generalizzazione della comunicazione con i dispositivi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 875                                                                                                                                          |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                              |

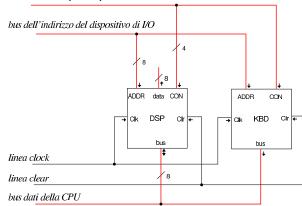

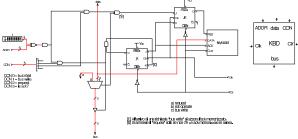

| Realizzazione dei dispositivi di I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 876                                                                                                                                          |

| Realizzazione dei dispositivi di I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 878                                                                                                                                          |

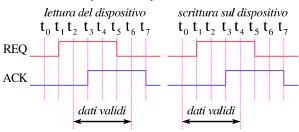

| Aspetto e funzionamento esteriore delle interfacce sincrone Interfaccia sincrona della tastiera  Interfaccia sincrona dello schermo                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 878<br>879<br>880                                                                                                                            |

| Aspetto e funzionamento esteriore delle interfacce sincrone Interfaccia sincrona della tastiera Interfaccia sincrona dello schermo Il bus della CPU con i dispositivi di I/O                                                                                                                                                                                                                                                                                                                                                                                                                      | 878<br>879<br>880<br>881                                                                                                                     |

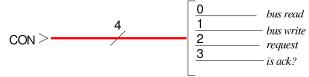

| Aspetto e funzionamento esteriore delle interfacce sincrone Interfaccia sincrona della tastiera Interfaccia sincrona dello schermo Il bus della CPU con i dispositivi di I/O Istruzione «out»                                                                                                                                                                                                                                                                                                                                                                                                     | 878<br>879<br>880<br>881<br>883                                                                                                              |

| Aspetto e funzionamento esteriore delle interfacce sincrone Interfaccia sincrona della tastiera Interfaccia sincrona dello schermo Il bus della CPU con i dispositivi di I/O Istruzione «out» Istruzione «in»                                                                                                                                                                                                                                                                                                                                                                                     | 878<br>879<br>880<br>881<br>.883<br>.884                                                                                                     |

| Aspetto e funzionamento esteriore delle interfacce sincrone Interfaccia sincrona della tastiera Interfaccia sincrona dello schermo Il bus della CPU con i dispositivi di I/O Istruzione «out»                                                                                                                                                                                                                                                                                                                                                                                                     | 878<br>879<br>880<br>881<br>.883<br>.884                                                                                                     |

| Aspetto e funzionamento esteriore delle interfacce sincrone Interfaccia sincrona della tastiera Interfaccia sincrona dello schermo Il bus della CPU con i dispositivi di I/O Istruzione «out» Istruzione «in»                                                                                                                                                                                                                                                                                                                                                                                     | 878<br>879<br>880<br>881<br>883<br>884                                                                                                       |

| Aspetto e funzionamento esteriore delle interfacce sincrone Interfaccia sincrona della tastiera Interfaccia sincrona dello schermo Il bus della CPU con i dispositivi di I/O Istruzione «out» Istruzione «in»  Versione I: ottimizzazione  Registri uniformi RAM                                                                                                                                                                                                                                                                                                                                  | 878<br>879<br>880<br>881<br>883<br>884<br>885<br>885                                                                                         |

| Aspetto e funzionamento esteriore delle interfacce sincrone Interfaccia sincrona della tastiera Interfaccia sincrona dello schermo Il bus della CPU con i dispositivi di I/O Istruzione «out» Istruzione «in»  Versione I: ottimizzazione  Registri uniformi RAM Modulo «SEL»                                                                                                                                                                                                                                                                                                                     | 878<br>879<br>880<br>881<br>883<br>884<br>885<br>885<br>886<br>888                                                                           |

| Aspetto e funzionamento esteriore delle interfacce sincrone Interfaccia sincrona della tastiera Interfaccia sincrona dello schermo Il bus della CPU con i dispositivi di I/O Istruzione «out» Istruzione «in»  Versione I: ottimizzazione  Registri uniformi RAM Modulo «SEL» ALU                                                                                                                                                                                                                                                                                                                 | 878<br>879<br>880<br>881<br>883<br>884<br>885<br>885<br>886<br>888                                                                           |

| Aspetto e funzionamento esteriore delle interfacce sincrone Interfaccia sincrona della tastiera Interfaccia sincrona dello schermo Il bus della CPU con i dispositivi di I/O Istruzione «out» Istruzione «in»  Versione I: ottimizzazione  Registri uniformi RAM Modulo «SEL» ALU Terminale                                                                                                                                                                                                                                                                                                       | 878<br>879<br>880<br>881<br>.883<br>.884<br>.885<br>.885<br>.885<br>.888<br>.888                                                             |

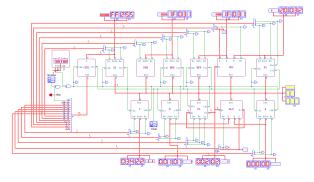

| Aspetto e funzionamento esteriore delle interfacce sincrone Interfaccia sincrona della tastiera Interfaccia sincrona dello schermo Il bus della CPU con i dispositivi di I/O Istruzione «out» Istruzione «in»  Versione I: ottimizzazione  Registri uniformi RAM Modulo «SEL» ALU Terminale Unità di controllo                                                                                                                                                                                                                                                                                    | 878<br>879<br>880<br>881<br>.883<br>.884<br>.885<br>.885<br>.886<br>.888<br>.888<br>.888                                                     |

| Aspetto e funzionamento esteriore delle interfacce sincrone Interfaccia sincrona della tastiera Interfaccia sincrona dello schermo Il bus della CPU con i dispositivi di I/O Istruzione «out» Istruzione «in»  Versione I: ottimizzazione  Registri uniformi RAM Modulo «SEL» ALU Terminale Unità di controllo Memorie, campi, argomenti e codici operativi                                                                                                                                                                                                                                       | 878<br>879<br>880<br>881<br>.883<br>.884<br>.885<br>.885<br>.885<br>.886<br>.888<br>.888<br>.888<br>.891                                     |

| Aspetto e funzionamento esteriore delle interfacce sincrone Interfaccia sincrona della tastiera Interfaccia sincrona dello schermo Il bus della CPU con i dispositivi di I/O Istruzione «out» Istruzione «in»  Versione I: ottimizzazione  Registri uniformi RAM Modulo «SEL» ALU Terminale Unità di controllo Memorie, campi, argomenti e codici operativi Microcodice                                                                                                                                                                                                                           | 878<br>879<br>880<br>881<br>.883<br>.884<br>.885<br>.885<br>.886<br>.888<br>.888<br>.899                                                     |

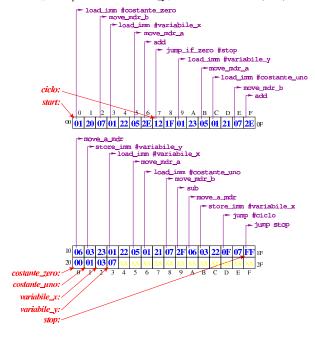

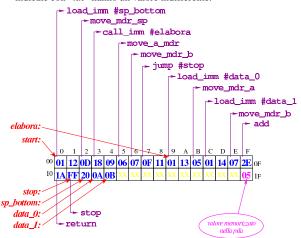

| Aspetto e funzionamento esteriore delle interfacce sincrone Interfaccia sincrona della tastiera Interfaccia sincrona dello schermo Il bus della CPU con i dispositivi di I/O Istruzione «out» Istruzione «in»  Versione I: ottimizzazione  Registri uniformi RAM Modulo «SEL»  ALU Terminale Unità di controllo Memorie, campi, argomenti e codici operativi Microcodice Macrocodice: chiamata di una routine                                                                                                                                                                                     | 878<br>879<br>880<br>881<br>883<br>884<br>885<br>886<br>888<br>888<br>891<br>893<br>907                                                      |

| Aspetto e funzionamento esteriore delle interfacce sincrone Interfaccia sincrona della tastiera Interfaccia sincrona dello schermo Il bus della CPU con i dispositivi di I/O Istruzione «out» Istruzione «in»  Versione I: ottimizzazione  Registri uniformi RAM Modulo «SEL» ALU Terminale Unità di controllo Memorie, campi, argomenti e codici operativi Microcodice                                                                                                                                                                                                                           | 878<br>879<br>880<br>881<br>883<br>884<br>885<br>885<br>886<br>888<br>889<br>891<br>893<br>907<br>0                                          |

| Aspetto e funzionamento esteriore delle interfacce sincrone Interfaccia sincrona della tastiera Interfaccia sincrona dello schermo Il bus della CPU con i dispositivi di I/O Istruzione «out» Istruzione «in»  Versione I: ottimizzazione  Registri uniformi RAM Modulo «SEL»  ALU Terminale Unità di controllo Memorie, campi, argomenti e codici operativi Microcodice Macrocodice: chiamata di una routine Macrocodice: inserimento da tastiera e visualizzazione sull                                                                                                                         | 878<br>879<br>880<br>881<br>.883<br>.884<br>.885<br>.885<br>.886<br>.888<br>.899<br>.907<br>0                                                |

| Aspetto e funzionamento esteriore delle interfacce sincrone Interfaccia sincrona della tastiera Interfaccia sincrona dello schermo Il bus della CPU con i dispositivi di I/O Istruzione «out» Istruzione «in»  Versione I: ottimizzazione  Registri uniformi RAM Modulo «SEL»  ALU Terminale Unità di controllo Memorie, campi, argomenti e codici operativi Microcodice Macrocodice: chiamata di una routine Macrocodice: inserimento da tastiera e visualizzazione sull schermo                                                                                                                 | 878<br>879<br>880<br>881<br>.883<br>.884<br>.885<br>.885<br>.886<br>.888<br>.891<br>.907<br>o<br>.907                                        |

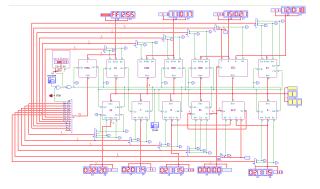

| Aspetto e funzionamento esteriore delle interfacce sincrone Interfaccia sincrona della tastiera Interfaccia sincrona dello schermo Il bus della CPU con i dispositivi di I/O Istruzione «out» Istruzione «in»  Versione I: ottimizzazione Registri uniformi RAM Modulo «SEL» ALU Terminale Unità di controllo Memorie, campi, argomenti e codici operativi Microcodice Macrocodice: chiamata di una routine Macrocodice: inserimento da tastiera e visualizzazione sull schermo  Versione J: ottimizzazione bis Versione K: 16 bit «little-endian»                                                | 878<br>879<br>880<br>881<br>.883<br>.884<br>.885<br>.885<br>.886<br>.888<br>.891<br>.893<br>.907<br>0<br>.907<br>.909<br>911                 |

| Aspetto e funzionamento esteriore delle interfacce sincrone Interfaccia sincrona della tastiera Interfaccia sincrona dello schermo Il bus della CPU con i dispositivi di I/O Istruzione «out» Istruzione «in»  Versione I: ottimizzazione  Registri uniformi RAM Modulo «SEL» ALU Terminale Unità di controllo Memorie, campi, argomenti e codici operativi Microcodice Macrocodice: chiamata di una routine Macrocodice: inserimento da tastiera e visualizzazione sull schermo Versione J: ottimizzazione bis                                                                                   | 878<br>879<br>880<br>881<br>.883<br>.884<br>.885<br>.885<br>.886<br>.888<br>.899<br>.907<br>o 907<br>.909<br>911                             |

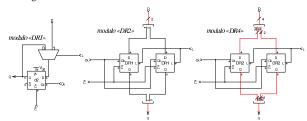

| Aspetto e funzionamento esteriore delle interfacce sincrone Interfaccia sincrona della tastiera Interfaccia sincrona dello schermo Il bus della CPU con i dispositivi di I/O Istruzione «out» Istruzione «in»  Versione I: ottimizzazione  Registri uniformi RAM Modulo «SEL»  ALU Terminale Unità di controllo Memorie, campi, argomenti e codici operativi Microcodice Macrocodice: chiamata di una routine Macrocodice: inserimento da tastiera e visualizzazione sull schermo  Versione J: ottimizzazione bis Versione K: 16 bit «little-endian» Registri a 16 bit                            | 878<br>879<br>880<br>881<br>.883<br>.884<br>.885<br>.885<br>.886<br>.888<br>.899<br>.907<br>o<br>.907<br>.909<br>911<br>.911                 |

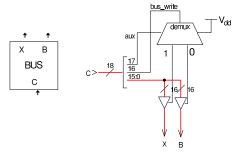

| Aspetto e funzionamento esteriore delle interfacce sincrone Interfaccia sincrona della tastiera Interfaccia sincrona dello schermo Il bus della CPU con i dispositivi di I/O Istruzione «out» Istruzione «in»  Versione I: ottimizzazione  Registri uniformi RAM Modulo «SEL»  ALU Terminale Unità di controllo Memorie, campi, argomenti e codici operativi Microcodice Macrocodice: chiamata di una routine Macrocodice: inserimento da tastiera e visualizzazione sull schermo  Versione J: ottimizzazione bis  Versione K: 16 bit «little-endian»  Registri a 16 bit Modulo «BUS»             | 878<br>879<br>880<br>881<br>.883<br>.884<br>.885<br>.885<br>.886<br>.888<br>.899<br>.907<br>o<br>.907<br>.909<br>911<br>.911<br>.913         |

| Aspetto e funzionamento esteriore delle interfacce sincrone Interfaccia sincrona della tastiera Interfaccia sincrona dello schermo Il bus della CPU con i dispositivi di I/O Istruzione «out» Istruzione «in»  Versione I: ottimizzazione  Registri uniformi RAM Modulo «SEL» ALU Terminale Unità di controllo Memorie, campi, argomenti e codici operativi Microcodice Macrocodice: chiamata di una routine Macrocodice: inserimento da tastiera e visualizzazione sull schermo  Versione J: ottimizzazione bis  Versione K: 16 bit «little-endian»  Registri a 16 bit Modulo «BUS» Modulo «ALU» | 878<br>879<br>880<br>881<br>.883<br>.884<br>.885<br>.885<br>.886<br>.888<br>.891<br>.907<br>0<br>.907<br>.909<br>911<br>.911<br>.913<br>.913 |

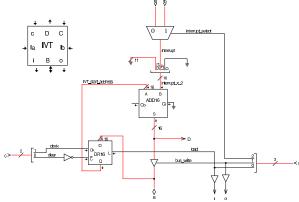

| Modulo «IVT»                                      | 920             |

|---------------------------------------------------|-----------------|

| Modulo «CTRL»                                     | 921             |

| Codici operativi                                  | 923             |

| Microcodice                                       | 934             |

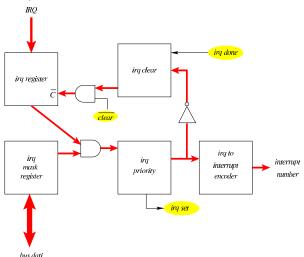

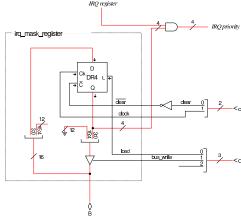

| Gestione delle interruzioni                       | 942             |

| Orologio: modulo «RTC»                            | 944             |

| Modulo «TTY»                                      | 944             |

| Modulo «HDD»                                      | 945             |

| Macrocodice: esempio di uso del terminale con 947 | le interruzioni |

| Riferimenti                                       | 949             |

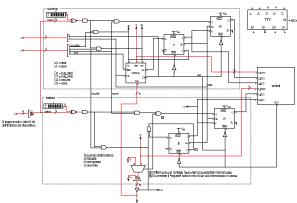

Viene qui introdotto lo sviluppo di una CPU dimostrativa, aggiungendo progressivamente componenti e funzioni, fino ad arrivare a un elaboratore molto semplice. Inizialmente si tratta solo di una CPU con registri a 8 bit, inclusi quelli relativi all'indirizzamento della memoria RAM, la quale è limitata così a un massimo di 256 byte.

816

Versione A: caricamento ed esecuzione del codice

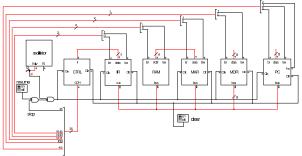

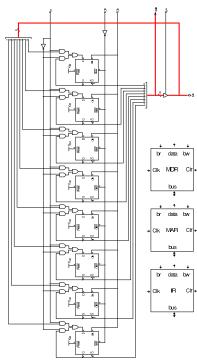

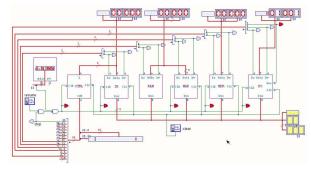

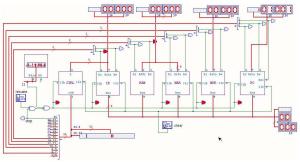

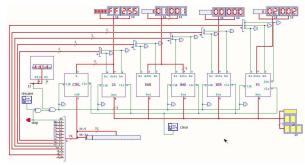

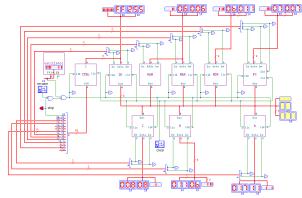

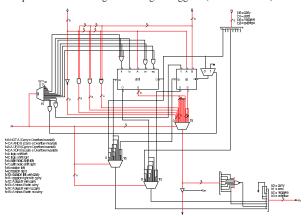

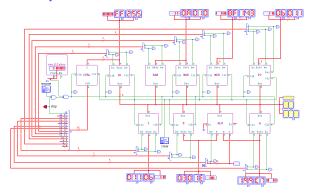

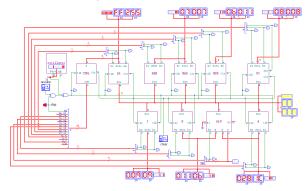

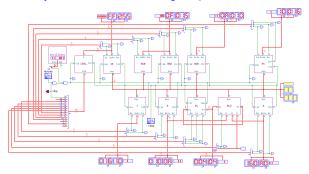

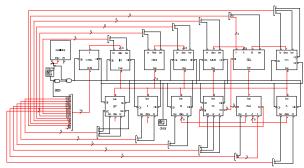

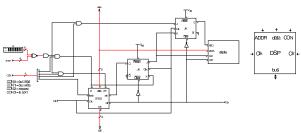

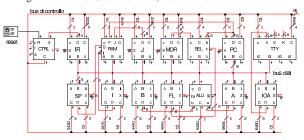

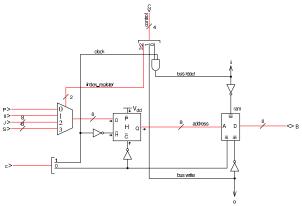

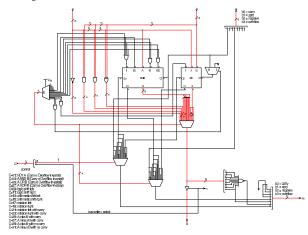

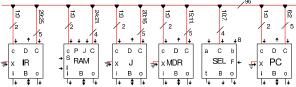

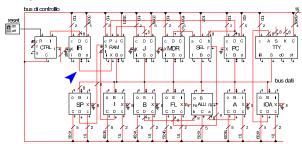

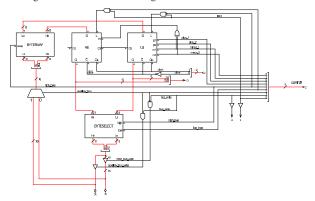

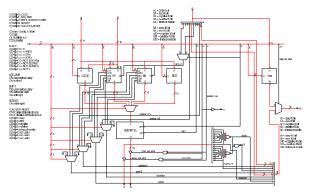

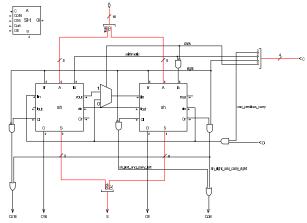

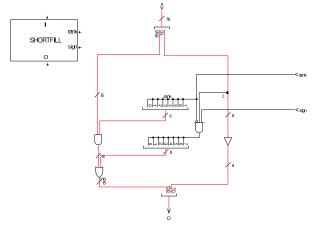

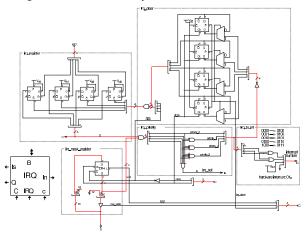

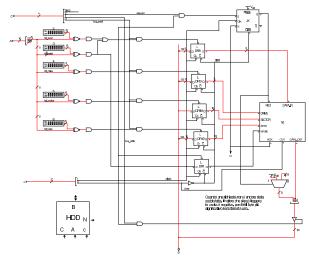

Nella sua prima versione, la CPU si compone soltanto di registri utili ad accedere alla memoria per leggere il codice operativo da eseguire, come di vede nella figura successiva.

Figura u106.1. Il bus della CPU nella sua prima fase realizzativa.

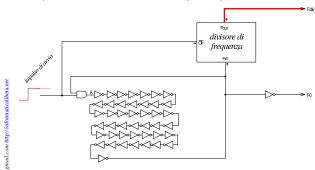

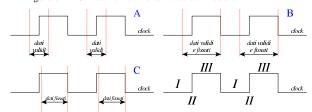

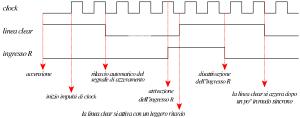

Il modulo più semplice che si può analizzare è l'oscillatore che serve a produrre il segnale di clock. Si tratta di un oscillatore costruito con una serie di porte logiche invertenti, per creare un ritardo di propagazione sufficiente a produrre un'oscillazione a una frequenza gestibile. Per attivare l'oscillazione si richiede un impulso iniziale che, dopo una breve pausa a zero, si attiva stabilmente. La figura successiva mostra l'oscillatore e l'impulso di avvio necessario per l'attivazione. È importante osservare che la serie di porte invertenti deve essere in numero dispari, come se si trattasse di una sola porta invertente, ma con un lungo ritardo di propagazione. Il risultato viene poi passato a un divisore di frequenza, composto in questo caso da una catena di flip-flop T, sincroni, in modo da non sfasare l'oscillazione a ogni divisione; in uscita si hanno tante linee raggruppate assieme, ognuna delle quali permette di prelevare un'oscillazione a una frequenza differente. Il divisore di frequenza è inizializzato dallo stesso impulso iniziale, il quale parte da uno stato a zero. Nel caso degli esempi viene usata una frequenza molto bassa, corrispondente all'ultimo stadio di divisione.

Figura u106.2. Oscillatore utilizzato per il segnale di clock.

Figura u106.3. Divisore utilizzato nel modulo dell'oscillatore.

L'impulso iniziale viene prodotto da un componente sintetizzato attraverso del codice Verilog, in quanto diversamente servirebbero

817

--- Copyright © Daniele Gia

componenti elettronici non logici e la loro trattazione esula dallo scopo di questo studio.

Figura u106.4. Codice Verilog per Tkgate, relativo al modulo di innesco dell'oscillazione: l'uscita è inizialmente a zero e dopo un breve istante passa a uno, rimanendo così stabilmente. Il tempo di attesa iniziale è configurabile attraverso il parametro  $\boldsymbol{W}$ .

```

module one_up #(.W(1000)) (Z);

output Z;

reg Z;

initial

begin

Z = 1'b0;

$tkg$wait(W);

Z = 1'b1;

end

endmodule

```

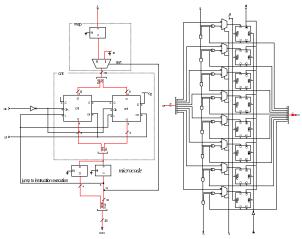

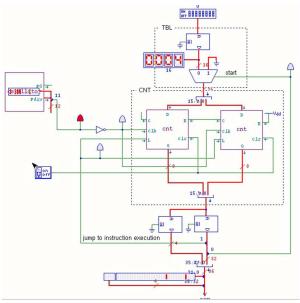

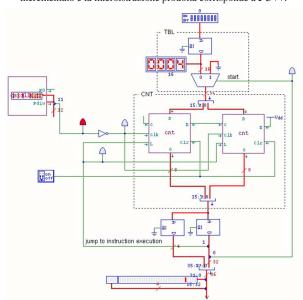

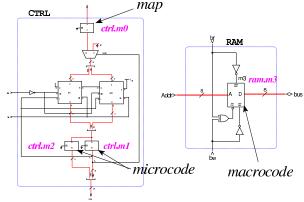

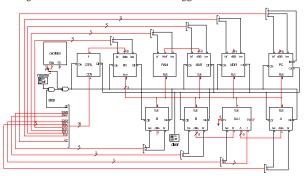

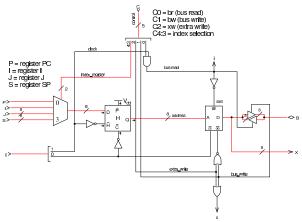

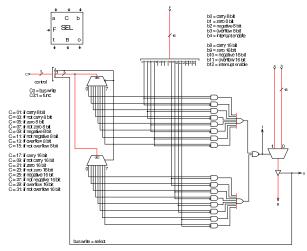

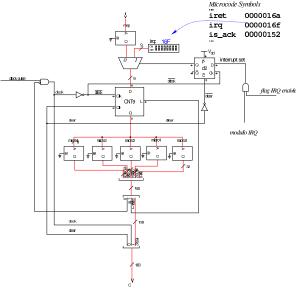

L'unità di controllo, contenuta nel modulo CTRL, è molto simile a quella descritta nella sezione  ${\tt u0.3}$ , con la differenza che l'ingresso è individuato dalla variabile  ${\it I}$  a 8 bit (la lettera «I» sta per «istruzione») e che l'uscita ha un rango molto maggiore, costringendo a utilizzare due unità di memoria in parallelo. Il contatore che serve a scandire le istruzioni nel blocco finale di memoria è complessivamente a 16 bit, ma per convenienza, ne sono stati usati due da 8 in cascata

L'ingresso *I* dell'unità di controllo è alimentato dal contenuto del registro *IR* (*instruction register*).

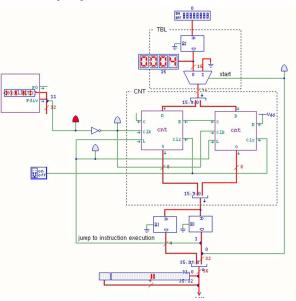

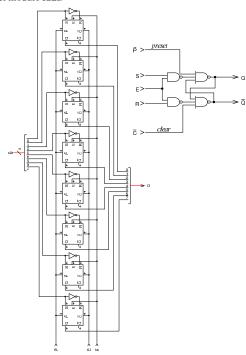

Figura u106.5. Unità di controllo, evidenziando a destra la struttura del modulo ent che rappresenta un contatore, basato su flip-flop D, estensibile per ottenere ranghi maggiori.

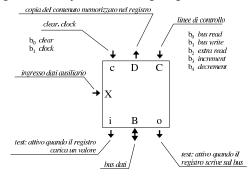

I moduli TR, MAR e MDR, sono registri semplici, costruiti con flipflop D, connessi al bus attraverso dei buffer a tre stati, dai quali è possibile prelevare copia del valore memorizzato da un'uscita supplementare, denominata data. Il registro IR (instruction register), a cui si è già accennato, ha lo scopo di conservare il codice operativo che l'unità di controllo deve eseguire; il registro MAR (memory address register) ha lo scopo di conservare l'indirizzo di memoria a cui si vuole accedere; il registro MDR (memory data register) serve ad accumulare quanto viene letto dalla memoria per qualche motivo o ciò che vi deve essere scritto.

Figura u106.6. Registri IR, MAR e MDR.

Il modulo PC è un registro simile agli altri, con la differenza che può incrementare il valore che contiene quando è attivo l'ingresso *Inc*. Il registro *PC* (*program counter*) ha lo scopo di contenere l'indirizzo di memoria del codice successivo da eseguire.

Figura u106.7. Registro contatore PC.

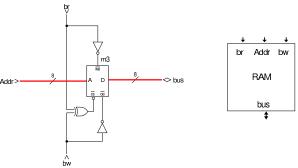

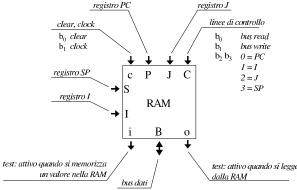

Il modulo RAM è sostanzialmente differente dagli altri, in quanto racchiude la memoria RAM usata dalla CPU. A tale memoria si accede attraverso l'indirizzo fornito tramite l'ingresso *Addr*, a 8 bit, e anche il contenuto della memoria è organizzato a celle da 8 bit. Il modulo condivide con gli altri gli ingressi di controllo dell'accesso

al bus; tuttavia, quando il modulo riceve l'indirizzo ed è abilitata la lettura dal bus, il valore contenuto in memoria viene aggiornato subito (salvo il ritardo di propagazione), senza attendere l'impulso di clock.

Il modulo RAM riceve l'indirizzo dal registro MAR (memory address register), il quale è così dedicato a contenere e conservare l'indirizzo di memoria a cui si vuole accedere.

Figura u106.8. Modulo RAM. La rete logica che controlla gli ingressi br e bw, serve a impedire che si possa mettere in pratica la lettura e scrittura simultanea del bus.

La prima cosa di cui si deve occupare la struttura appena descritta, consiste nel caricamento di un'istruzione, seguito poi dall'esecuzione della stessa: ciò è noto come *ciclo di caricamento* (*fetch*). Nella struttura in questione, il registro *PC* contiene l'indirizzo dell'istruzione da eseguire: questo valore deve essere trasferito nel registro *MAR* e il registro *PC* viene incrementato; dalla memoria RAM si ottiene l'istruzione contenuta nell'indirizzo *MAR* che viene copiata nel registro *IR*. Ciò si può rappresentare sinteticamente come segue:

- 1. MAR = PC

- 2. *PC*++

- 3. IR = RAM[MAR]

Le figure successive mostrano proprio questi tre passaggi, evidenziando i valori degli ingressi *br*, *bw* e *Inc*, attraverso dei LED che diventano rossi nel momento dell'attivazione della linea a cui sono connessi. Le figure mostrano sempre solo il momento in cui il segnale di clock diventa attivo.

Figura u106.9. Prima fase: si richiede al registro *PC* di inviare il suo valore al bus e al registro *MAR* di leggerlo. Si attua in pratica l'operazione *MAR=PC*.

Figura u106.10. Seconda fase: si richiede al registro *PC* di incrementarsi di una unità. Si attua in pratica l'operazione *PC*++.

Figura u106.11. Terza fase: si richiede alla RAM di inviare il valore corrispondente all'indirizzo recepito dal registro *MDR* al bus e al registro *IR* di accumulare questo valore. Si attua in pratica l'operazione *IR=RAM[MAR]*.

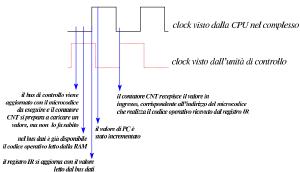

All'interno dell'unità di controllo (il modulo CTRL) il tempo è scandito allo stesso modo, a parte il fatto che i contatori *cnt* sono pilotati da un segnale di clock invertito, per anticipare l'attivazione delle linee di controllo rispetto all'impulso relativo alla gestione del bus dati. Inizialmente i contatori dell'unità di controllo si trovano a essere azzerati e per questo vanno a ricercare nella memoria sottostante la prima microistruzione, corrispondente alla richiesta di eseguire l'operazione *MAR=PC*. Successivamente il complesso dei due contatori *cnt* viene incrementato e ciò fa passare alla seconda microistruzione, corrispondente alla richiesta di incremento del registro *PC*. Nel terzo istante si ha un incremento ulteriore, facendo emergere la microistruzione *IR=RAM[MAR]*.

Figura u106.12. Prima fase: i contatori dell'unità di controllo sono azzerati e la microistruzione iniziale corrisponde a *MAR=PC*.

Figura u106.13. Seconda fase: il complesso dei contatori è stato incrementato e la microistruzione prodotta corrisponde a PC++.

Figura u106.14. Terza fase: il complesso dei contatori è stato incrementato e la microistruzione prodotta corrisponde a *IR=RAM[MAR]*.

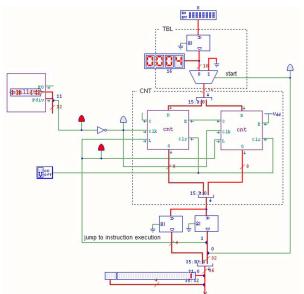

A questo punto, l'unità di controllo dispone dell'istruzione da eseguire nell'ingresso I ed è pronta per recepirla. Per farlo, la microistruzione successiva richiede al contatore interno di accettare il valore in ingresso. Questo valore corrisponde al contenuto della memoria m0, la quale tratta l'istruzione in ingresso come indirizzo, dal quale produce a sua volta l'indirizzo del microcodice successivo a cui saltare. Negli esempi delle figure, l'istruzione in questione corrisponde al codice operativo  $00000000_2$ , ovvero all'istruzione nulla  $(not\_operate)$ .

Figura u106.15. Quarta fase: i contatori dell'unità di controllo sono caricati con il valore proveniente dalla memoria che traduce l'istruzione in indirizzo del microcodice.

Figura u106.16. Fase conclusiva: i contatori dell'unità di controllo sono stati incrementati e puntano alla microistruzione successiva. Dal momento che l'istruzione originale (not\_operate) non richiedeva lo svolgimento di alcuna operazione nel bus dati, ci si trova al termine della procedura per tale istruzione, incontrando la microistruzione che richiede al complesso di contatori dell'unità di controllo di azzerarsi. L'azzeramento avviene facendo caricare ai contatori il valore zero, tramite il multiplatore che controlla l'ingresso di tali contatori.

Dopo l'azzeramento dei contatori dell'unità di controllo, si ricomincia dal microcodice iniziale (le prime tre fasi) con il quale si richiede il caricamento di una nuova istruzione.

Va osservato che durante la quarta fase (salto al microcodice di esecuzione dell'istruzione richiesta) e durante la fase conclusiva (salto al microcodice iniziale che attua il ciclo di caricamento), nel bus dati non succede nulla.

Figura u106.17. Durante la fase di salto al microcodice di esecuzione dell'istruzione richiesta e durante il salto al microcodice del ciclo di caricamento, nel bus dati non succede nulla.

Per fermare il funzionamento del circuito descritto, esiste l'istruzione stop (111111111<sub>2</sub>), con la quale viene fermato il segnale di clock. La figura successiva mostra questa situazione.

Figura u106.18. La situazione in cui si trova il bus dati quando viene eseguita l'istruzione stop: la linea di controllo *CON*<sub>35</sub> si attiva e va a bloccare il segnale di clock. Per far riprendere l'esecuzione da quel punto, superando lo stop, occorrerebbe intervenire nell'interruttore situato vicino al LED che risulta attivo.

Dovrebbero essere disponibili due video, nei quali si dimostra l'esecuzione di due sole istruzioni (macroistruzioni):

#### 1. not\_operate

#### 2. stop

Il primo video <a href="http://www.youtube.com/watch?v=Z8bTO8WjYYc">http://www.youtube.com/watch?v=Z8bTO8WjYYc</a> mostra ciò che accade nel bus dati; il secondo, invece, mostra l'interno dell'unità di controllo <a href="http://www.youtube.com/watch?v=pPxCQz7IFbM">http://www.youtube.com/watch?v=pPxCQz7IFbM</a>.

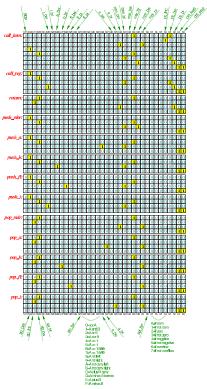

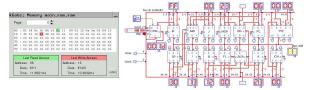

Per descrivere il contenuto delle memorie, incluso quello della memoria RAM, viene usato un file sorgente scritto secondo la sintassi adatta a 'gmac' di Tkgate 2. Le prime direttive descrivono i banchi di memoria, i quali sono organizzati così: *ctrl.m0* corrisponde alla prima memoria in alto dell'unità di controllo; *ctrl.m1* e *ctrl.m2* sono le due memorie che contengono il microcodice e che si trovano in basso nello schema dell'unità di controllo; *ram.m3* è invece la memoria contenuta nel modulo RAM del bus dati e ospita il macrocodice che inizialmente si limita solo a not\_operate e stop.

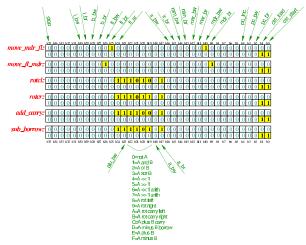

Figura u106.20. Dove si trovano concretamente i banchi di memoria.

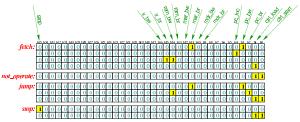

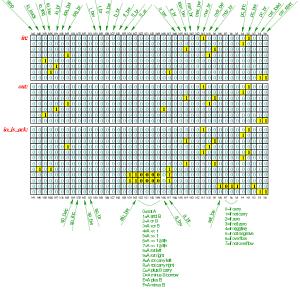

Si passa quindi alla descrizione dei campi in cui è suddivisa ogni cella di memoria che rappresenta il microcodice (*ctrl.m1* e *ctrl.m2*). Per esempio, il bit meno significativo si chiama *ctrl\_start*, mentre il più significativo si chiama *stop*. Va osservato che non sono descritti tutti i 36 bit della cella che rappresenta una microistruzione, perché al momento il codice si limita a rappresentare la riduzione della CPU nella sua prima versione.

```

field ctrl_start[0];

// parte dall'indirizzo 0

field ctrl load[1];

// carica l'indirizzo nel contatore.

field pc br[2];

// PC <-- bus

// PC --> bus

field pc bw[3];

// PC++

field pc Inc[4];

field mdr_br[9];

// MDR <-- bus

field mdr bw[10];

// MDR --> bus

field mar_br[11];

// MAR <-- bus

field mar_bw[12];

// MAR --> bus

field ram_br[13];

// RAM[mar] <-- bus

field ram_bw[14];

// RAM[mar] --> bus

field ir_br[15];

// IR <-- bus

// IR --> bus

field ir_bw[16];

field stop[35];

// stop clock

```

Vengono poi descritti i tipi di operandi che possono avere le istruzioni (le macroistruzioni). Si prevede di gestire istruzioni senza operandi, oppure con un solo operando di 8 bit. Il significato della sintassi utilizzata per descrivere il tipo  $op_{-}0$  e il tipo  $op_{-}1$ , va approfondito, eventualmente, nella documentazione di Tkgate.

Si passa poi alla descrizione dei codici operativi; per esempio, si vede che l'istruzione not\_operate corrisponde al codice zero (000000002), mentre l'istruzione jump ha il codice 15 (00001111<sub>2</sub>). Va osservato che nel primo caso (not\_operate) non ci sono argomenti, mentre nel secondo si richiede un argomento.

```

op not_operate {

map not_operate : 0;

+0[7:0]=0;

operands op_0;

};

op jump {

map jump : 15;

+0[7:0]=15;

operands op_1;

};

op stop {

map stop : 255;

+0[7:0]=255;

operands op_0;

};

```

Inizia quindi la definizione del microcodice, il quale viene collocato a partire dall'indirizzo zero della coppia di memorie *ctrl.m1* e *ctrl.m2*. Si può osservare che si inizia proprio dalla descrizione del ciclo di caricamento (*fetch*) che si conclude con il salto alla microistruzione che inizia la procedura che mette in pratica la macroistruzione recepita; inoltre, alla fine della descrizione di ogni macroistruzione (in forma di microcodice), viene richiesto di saltare nuovamente alla prima microistruzione, con la quale si ripete il ciclo di caricamento.

```

jump:

mar br pc bw;

// MAR = PC

// PC <-- RAM[MAR]

pc br ram bw;

ctrl_start ctrl_load;

// salta a «fetch»

11

stop:

// stop clock.

stop;

// Se il clock fosse

// riabilitato manualmente:

ctrl_start ctrl_load;

// salta a «fetch»

end

```

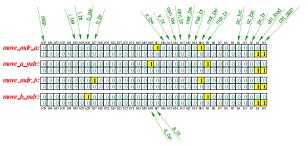

Figura u106.25. Corrispondenza con il contenuto della memoria che rappresenta il microcodice (la coppia *m1* e *m2* dell'unità di controllo).

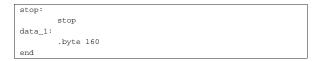

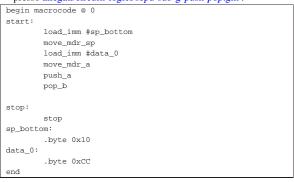

Infine, inizia il macrocodice, ovvero il codice assemblatore da immettere nella memoria RAM:

```

begin macrocode @ 0

start:

not_operate

stop

end

```

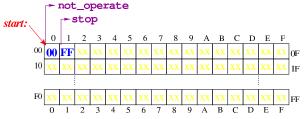

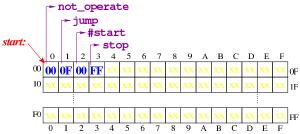

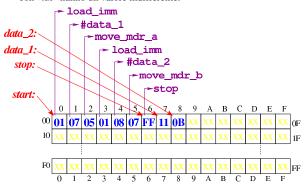

Figura u106.27. Macrocodice contenuto nella memoria RAM. Le celle indicate con «xx» hanno un valore indifferente.

Tabella u106.28. Elenco delle macroistruzioni di questa prima versione della CPU dimostrativa.

| Sintassi              | Descrizione                                                             |

|-----------------------|-------------------------------------------------------------------------|

| not_operate           | Non fa alcunché, limitandosi a passare all'istruzione successiva.       |

| jump <i>indirizzo</i> | Salta all'istruzione che si trova in memoria all'indirizzo specificato. |

| stop                  | Ferma l'afflusso degli impulsi di clock.                                |

Il file descritto dovrebbe essere disponibile all'indirizzo *allegati/circuiti-logici/scpu-sub-a.gm*. Per compilarlo con 'gmac' di Tkgate 2, si dovrebbe procedere con il comando successivo:

Il file 'scpu-sub-a.mem' che si ottiene è quello che serve a Tkgate 2 per caricare i contenuti delle memorie previste. Eventualmente, dovrebbe essere disponibile anche il file *allegati/circuiti-logici/scpu-sub-a.v* che contiene la rappresentazione completa di questa prima versione della CPU dimostrativa nel formato di Tkgate 2.

Prima di concludere la descrizione della versione iniziale della CPU dimostrativa, va osservato che esiste una terza istruzione che non è ancora stata usata in un esempio: jump. Questa si realizza semplicemente con i passaggi seguenti:

```

1. MAR = PC

```

#### 2. PC = RAM[MAR]

In pratica: nel registro *MAR* viene copiato l'indirizzo contenuto nel registro *PC*, il quale corrisponde all'indirizzo successivo all'istruzione appena letta e in corso di esecuzione (jump), ma il contenuto della memoria corrispondente a tale indirizzo, viene copiato di nuovo nel registro *PC* (senza incrementarlo).

L'istruzione jump precede un argomento, costituito dall'indirizzo a cui si vuole saltare incondizionatamente; pertanto, tale indirizzo si colloca subito dopo il codice dell'istruzione e viene letto attraverso l'indice del registro PC, come se si trattasse di un'istruzione; poi, però, il contenuto della memoria in corrispondenza di quell'indirizzo, non viene inviato al registro IR, ma viene immesso nuovamente nel registro PC, in maniera tale che la prossima istruzione a essere caricata sia quella a cui si vuole saltare.

A titolo di esempio, il macrocodice (ovvero il codice assemblatore) potrebbe essere modificato come segue:

```

begin macrocode @ 0

start:

not_operate

jump #start

stop

end

```

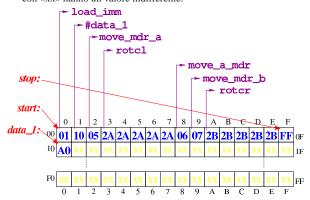

Figura u106.30. Contenuto della memoria RAM. Le celle indicate con «xx» hanno un valore indifferente.

Durante la compilazione, '#start' viene rimpiazzato dall'indirizzo corrispondente all'etichetta 'start:' che in pratica è semplicemente zero. Questo piccolo programma si limita a non fare nulla (not\_operate) e a ripeterlo indefinitivamente, tanto che l'istruzione stop non può mai essere eseguita. Le figure successive mostrano ciò che accade dopo l'esecuzione dell'istruzione not\_operate nel bus dati.

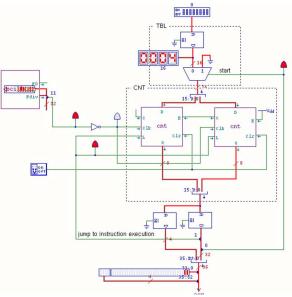

Figura u106.31. La situazione in cui si trova il bus dati quando è stata caricata l'istruzione jump e il registro PC, puntando all'indirizzo che segue l'istruzione jump, immette il suo valore nel registro MAR.

Figura u106.32. Il valore contenuto nella memoria, in corrispondenza dell'indirizzo di salto, viene immesso nel registro *PC*, facendo in modo che si riparta poi da quella posizione.

Dovrebbe essere disponibile un video che mostra l'esecuzione del macrocodice descritto: <a href="http://www.youtube.com/watch?v=Z8bTO8WjYYc">http://www.youtube.com/watch?v=Z8bTO8WjYYc</a>.

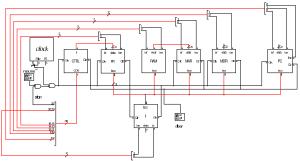

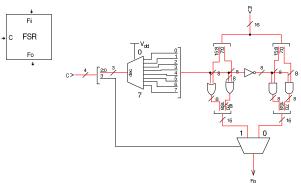

Nella seconda versione della CPU dimostrativa, viene aggiunto soltanto un registro speciale, denominato I, il cui scopo è quello di contenere un indice della memoria. Nello specifico, serve a poter leggere o scrivere nella memoria RAM, attraverso un indice che possa essere gestito. Il registro I è realizzato nello stesso modo di MDR, MAR e IR.

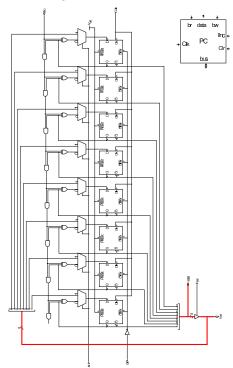

Figura u107.1. Il bus della CPU nella sua seconda fase realizzativa.

Nel codice che descrive i campi del bus di controllo, si aggiungono quelli seguenti, i quali servono specificatamente a gestire il registro

```

field i_br[29]; // I <-- bus

field i_bw[30]; // I --> bus

```

Nell'elenco dei codici operativi si aggiungono istruzioni nuove e lo stesso poi nella descrizione del microcodice:

```

op load_imm

map load_imm : 1;

// load from address #nn

+0[7:0]=1;

operands op_1;

};

op load_reg

map load_reg : 2;

// load from address %I

+0[7:0]=2;

operands op_0;

};

op store_imm {

map store_imm : 3;

// store to address #nn

+0[7:0]=3;

operands op_1;

op store req {

map store_reg : 4;

// store to address I

+0[7:0]=4;

operands op_0;

op move_mdr_i {

map move_mdr_i : 11;

// move MDR to I

+0[7:0]=11;

operands op_0;

op move_i_mdr {

map move_i_mdr : 12;

// move I to MDR

+0[7:0]=12;

operands op_0;

```

831

«a2» 2013.11.11 --- Copyright © Daniele Giacomini -- appunti2@gmail.com http://infoanaticalibera.

```

// quindi, non si può passare

// direttamente a MAR.

i br ram bw;

// I <-- RAM[MAR]

// MAR <-- I

mar br i bw;

// MDR <-- RAM[MAR]

mdr br ram bw;

ctrl start ctrl load;

// CNT <-- 0

load reg:

mar_br i_bw;

// MAR <-- I

mdr_br ram_bw;

// MDR <-- RAM[MAR]

ctrl_start ctrl_load;

// CNT <-- 0

store_imm:

mar_br pc_bw;

// MAR <-- PC

pc_Inc;

// PC++

i_br ram_bw;

// I <-- RAM[MAR]

mar_br i_bw;

// MAR <-- I

ram_br mdr_bw;

// RAM[MAR] <-- MDR

ctrl_start ctrl_load;

// CNT <-- 0

store req:

mar br i bw;

// MAR <-- I

ram br mdr bw;

// RAMIMAR1 <-- MDR

ctrl_start ctrl_load;

// CNT <-- 0

move_mdr_i:

i_br mdr_bw;

// I <-- MDR

ctrl_start ctrl_load;

// CNT <-- 0

move_i_mdr:

mdr_br i_bw;

// MDR <-- I

ctrl_start ctrl_load;

// CNT <-- 0

```

Figura u107.5. Corrispondenza con il contenuto della memoria che rappresenta il microcodice (la coppia m1 e m2 dell'unità di controllo).

Tabella u107.6. Elenco delle macroistruzioni aggiunte in questa versione della CPU dimostrativa.

| versione della CFO dilli   |                                                |  |

|----------------------------|------------------------------------------------|--|

| Sintassi                   | Descrizione                                    |  |

|                            | load immediate: carica nel registro MDR il     |  |

|                            | contenuto della cella di memoria che cor-      |  |

| load imm indirizzo         | risponde all'indirizzo indicato dall'argo-     |  |

| Toda_Ittill Man 1220       | mento. Contestualmente, il registro I viene    |  |

|                            | modificato e alla fine contiene l'indirizzo    |  |

|                            | di memoria in questione.                       |  |

|                            | load register: carica nel registro MDR il      |  |

| load_reg                   | contenuto della cella di memoria che cor-      |  |

| Todd_Icg                   | risponde all'indirizzo indicato dal valore     |  |

|                            | contenuto nel registro $I$ .                   |  |

|                            | store immediate: salva in memoria, all'in-     |  |

|                            | dirizzo specificato come argomento, il va-     |  |

| store_imm <i>indirizzo</i> | lore contenuto nel registro MDR. Conte-        |  |

|                            | stualmente, il registro $I$ viene modificato e |  |

|                            | alla fine contiene l'indirizzo di memoria in   |  |

|                            | questione.                                     |  |

| Sintassi   | Descrizione                                 |

|------------|---------------------------------------------|

|            | store register: salva in memoria, all'indi- |

| store_reg  | rizzo specificato dal registro I, il valore |

|            | contenuto nel registro MDR.                 |

| move mdr i | Copia il contenuto del registro MDR nel     |

| move_mar_1 | registro I.                                 |

| move i mdr | Copia il contenuto del registro I nel       |

| move_i_mai | registro MDR                                |

#### Istruzioni «load»

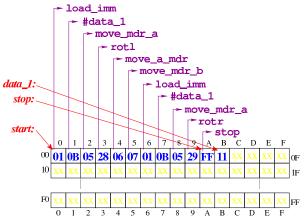

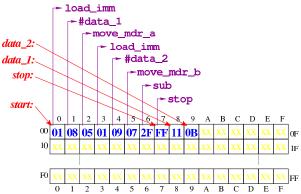

Come primo esempio viene proposto il macrocodice seguente:

```

begin macrocode @ 0

start:

load_imm #data_1

move_mdr_i

load_reg

stop:

stop

data_1:

.byte 3

end

```

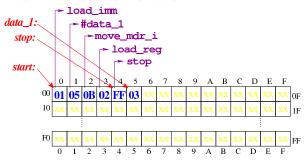

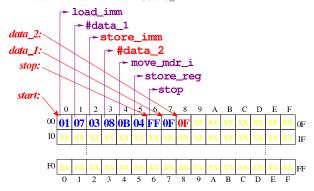

In pratica, viene caricato nel registro MDR il valore corrispondente all'indirizzo in cui si trova l'etichetta 'data\_1:' (facendo i conti si tratta dell'indirizzo 5); successivamente, il valore di MDR viene copiato nel registro I e quindi viene caricato nel registro MDR quanto contenuto nell'indirizzo di memoria corrispondente al valore di I: dal momento che a quel indirizzo si trova il valore 2, corrispondente al codice operativo dell'istruzione load\_reg, al termine, il registro MDR contiene tale valore. Il file completo che descrive le memorie per Tkgate dovrebbe essere disponibile all'indirizzo allegati/circuitilogici/scpu-sub-b.gm

Figura u107.8. Contenuto della memoria RAM. Le celle indicate con «xx» hanno un valore indifferente.

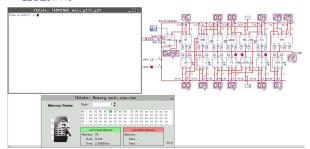

Figura u107.9. Situazione conclusiva del bus dati, dopo l'esecuzione delle istruzioni di caricamento. Video: http://www.youtube.com/watch?v=AXUSrH49cF49w

## Istruzioni «store»

Viene proposto un altro esempio di macrocodice, nel quale si sperimentano le istruzioni store\_imm e store\_reg:

```

begin macrocode @ 0

start:

load_imm #data_1

store_imm #data_2

move_mdr_i

store_reg

stop:

stop

data_1:

.byte 15

data_2:

.byte 0

end

```

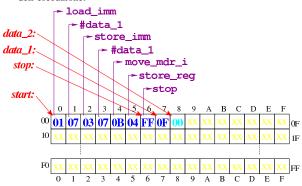

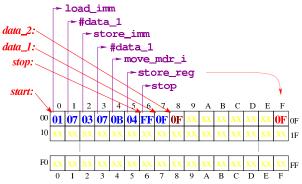

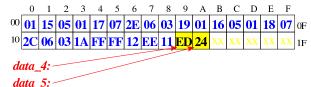

In questo caso, si carica nel registro *MDR* il valore contenuto in memoria in corrispondenza dell'etichetta 'data\_1:'; quindi si memorizza, in corrispondenza della posizione di memoria corrispondente all'etichetta 'data\_2:', il valore contenuto in *MDR* (in pratica, in quella destinazione che prima conteneva il valore zero, viene copiato il valore 15, ovvero 0F<sub>16</sub>); quindi il contenuto del registro *MDR* viene copiato nel registro *I* e poi viene memorizzato il contenuto di *MDR* (che è rimasto sempre 15) nella posizione di memoria corrispondente al valore del registro *I*. In pratica, alla fine si va a scrivere anche nella posizione 15 (0F<sub>16</sub>) della memoria, e ci si mette il valore 15

Figura u107.11. Contenuto della memoria RAM all'inizio dell'esecuzione.

Figura u107.12. Contenuto della memoria RAM dopo l'esecuzione dell'istruzione store\_imm.

834

Figura u107.13. Contenuto della memoria RAM al termine dell'esecuzione.

Figura u107.14. Situazione conclusiva del bus dati, dopo l'esecuzione delle istruzioni di memorizzazione. Video: http://www.youtube.com/watch?v=1Hxx3SR56hE56

u

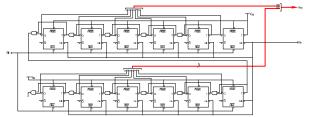

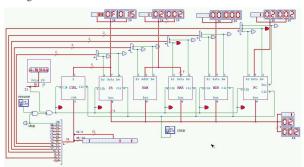

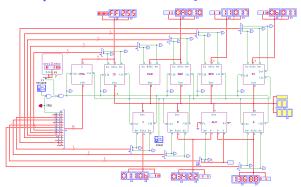

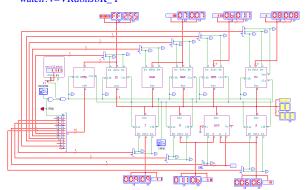

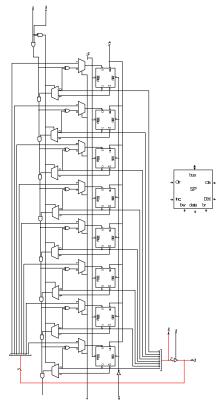

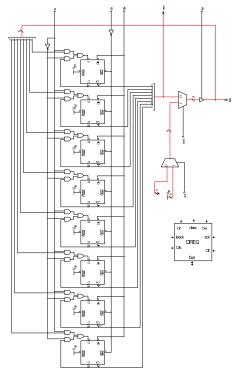

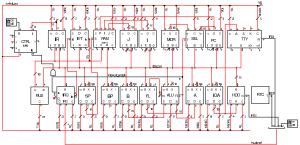

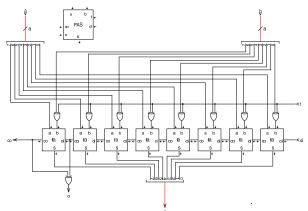

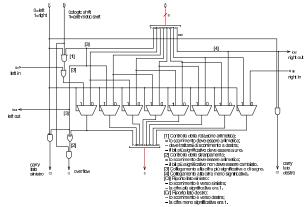

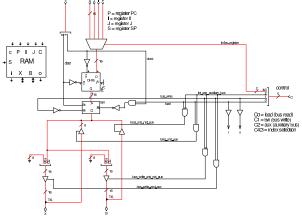

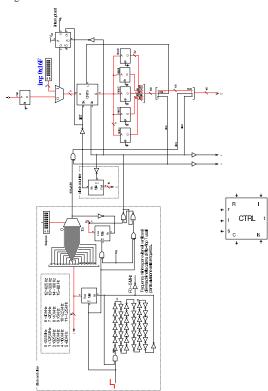

Nella terza versione della CPU dimostrativa, vengono aggiunti due registri che per il momento non hanno alcuno scopo particolare:  $A \in B$ . Tali registri sono realizzati nello stesso modo di I, MDR,  $MAR \in IR$

Figura u108.1. Il bus della CPU nella sua terza fase realizzativa.

Nel codice che descrive i campi del bus di controllo, si aggiungono quelli seguenti, i quali servono specificatamente a gestire i registri A e B:

Nell'elenco dei codici operativi si aggiungono istruzioni nuove e lo stesso poi nella descrizione del microcodice:

```

op move_mdr_a {

// move MDR to A

map move_mdr_a : 5;

+0[7:0]=5;

operands op_0;

op move_a_mdr {

map move_a_mdr : 6;

// move A to MDR

+0[7:0]=6;

operands op_0;

op move_mdr_b {

map move_mdr_b : 7;

// move MDR to B

+0[7:0]=7;

operands op_0;

op move_b_mdr {

map move_b_mdr : 8;

// move B to MDR

+0[7:0]=8;

operands op_0;

```

```

begin microcode @ 0

move_mdr_a:

// A <-- MDR

a br mdr bw;

ctrl_start ctrl_load;

// CNT <-- 0

move_a_mdr:

mdr_br a_bw;

// MDR <-- A

ctrl_start ctrl_load;

// CNT <-- 0

move_mdr_b:

// B <-- MDR

b_br mdr_bw;

ctrl_start ctrl_load;

// CNT <-- 0

move_b_mdr:

// MDR <-- B

mdr br b bw;

// CNT <-- 0

ctrl_start ctrl_load;

```

836 837

«a2» 2013.11.11 --- Copyright © Daniele Gia

Figura u108.5. Corrispondenza con il contenuto della memoria che rappresenta il microcodice (la coppia m1 e m2 dell'unità di controllo).

Tabella u108.6. Elenco delle macroistruzioni aggiunte in questa versione della CPU dimostrativa.

| versione dena er e dimostrativa. |                                         |

|----------------------------------|-----------------------------------------|

| Sintassi                         | Descrizione                             |

| move_mdr_a                       | Copia il contenuto del registro MDR nel |

|                                  | registro A.                             |

| move a mdr                       | Copia il contenuto del registro A nel   |

| move_a_mar                       | registro MDR.                           |

| move mdr b                       | Copia il contenuto del registro MDR nel |

| move_mar_b                       | registro B.                             |

| move_b_mdr                       | Copia il contenuto del registro B nel   |

|                                  | registro MDR.                           |

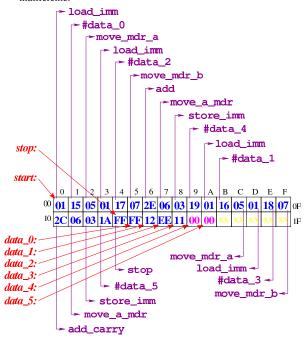

## Come esempio viene proposto il macrocodice seguente:

```

begin macrocode @ 0

start:

load_imm #data_1

move_mdr_a

load_imm #data_2

move_mdr_b

stop:

stop

data_1:

.byte 17

data_2:

.byte 11

end

```

In pratica, viene caricato nel registro *MDR* il valore corrispondente all'indirizzo in cui si trova l'etichetta 'data\_1:' (facendo i conti si tratta dell'indirizzo 7); successivamente, il valore di *MDR* viene copiato nel registro *A*; quindi viene caricato nel registro *MDR* quanto contenuto nell'indirizzo di memoria corrispondente all'etichetta 'data\_2:' (indirizzo 8) e poi copiato nel registro *B*. Il file completo che descrive le memorie per Tkgate dovrebbe essere disponibile all'indirizzo *allegati/circuiti-logici/scpu-sub-c.gm*

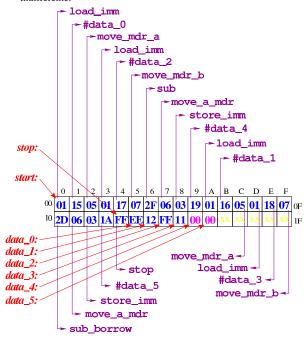

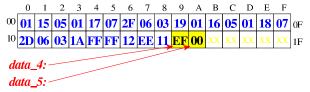

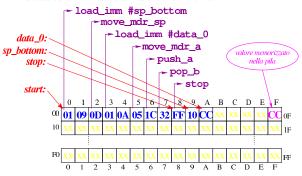

Figura u108.8. Contenuto della memoria RAM. Le celle indicate con «xx» hanno un valore indifferente.

Figura u108.9. Situazione conclusiva del bus dati, dopo l'esecuzione delle istruzioni copia nei registri  $A \in B$ . Video: http://www.youtube.com/watch?v=9qVsCKmxcdk

Dalle istruzioni introdotte in questa versione della CPU dimostrativa, si può intendere che i dati contenuti nei registri possano essere copiati soltanto con la mediazione del registro *MDR*; pertanto non esiste un'istruzione move\_a\_b. Questa è una semplificazione per evitare di dover dichiarare tante istruzioni nel macrocodice, ma in condizioni normali, tale scelta non sarebbe utile.

## Versione D: ALU

| Istruzione «not»           | 840 |

|----------------------------|-----|

| Istruzione «and»           | 846 |

| Istruzione «or»            | 847 |

| Istruzione «xor»           | 848 |

| Istruzioni «lshl» e «lshr» | 849 |

| Istruzioni «ashl» e «ashr» | 850 |

| Istruzioni «rotl» e «rotr» | 851 |

| Istruzione «add»           | 852 |

| Istruzione «sub»           | 853 |

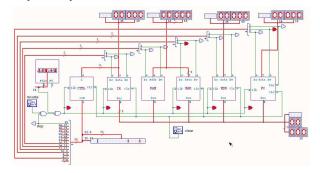

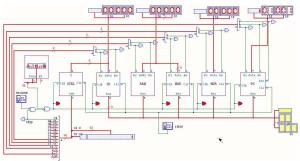

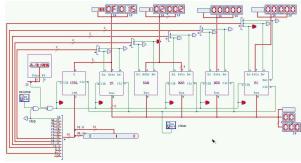

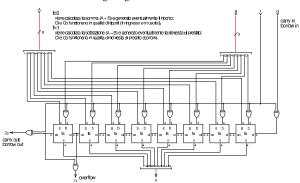

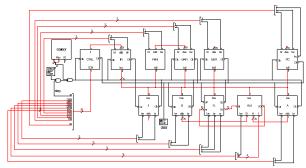

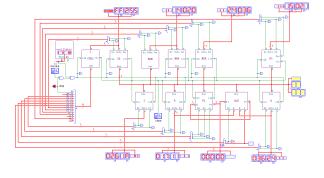

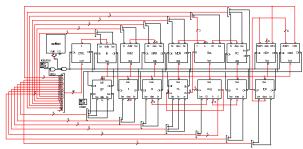

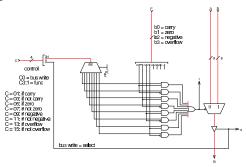

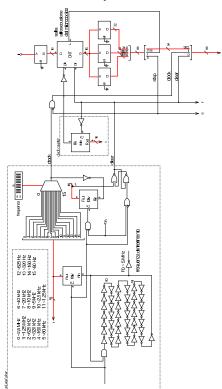

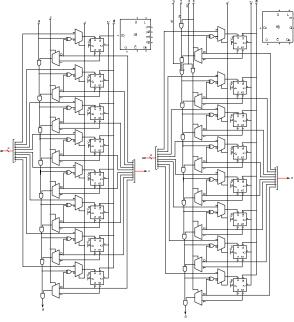

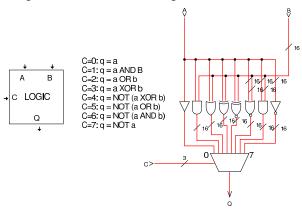

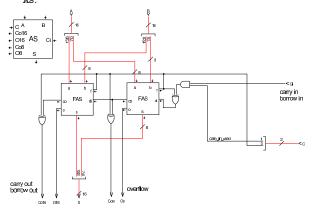

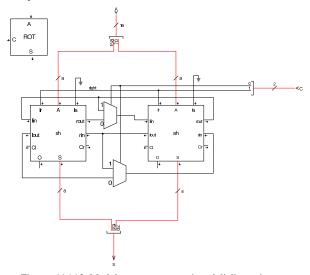

Nella quarta versione della CPU dimostrativa, viene aggiunta un'unità aritmetica, logica e di scorrimento (ALU), ma per il momento senza gestire gli indicatori (riporto, segno, zero e straripamento).

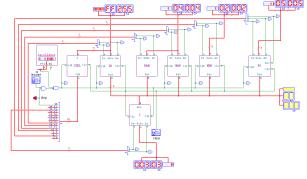

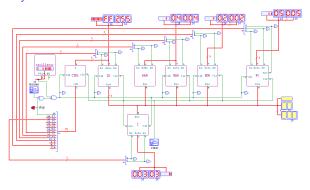

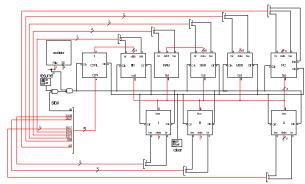

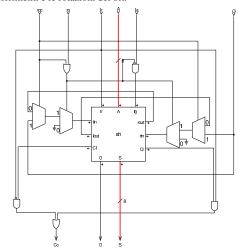

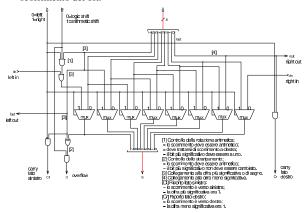

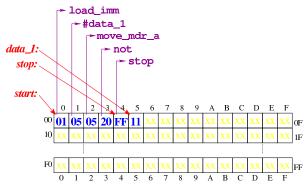

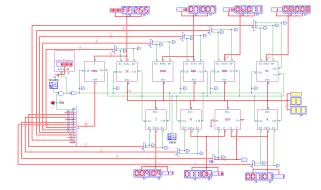

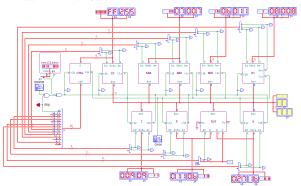

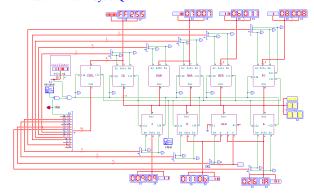

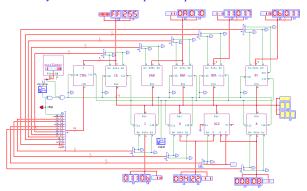

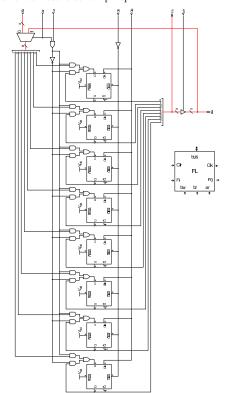

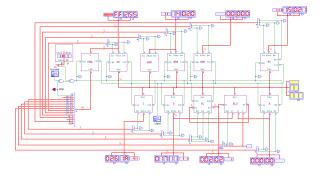

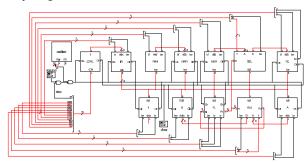

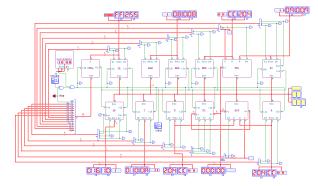

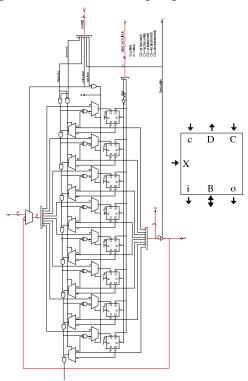

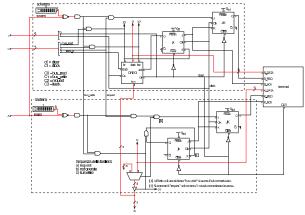

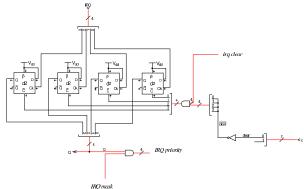

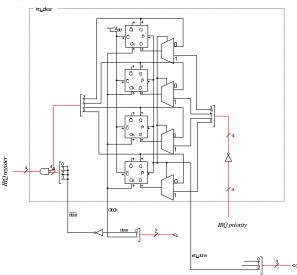

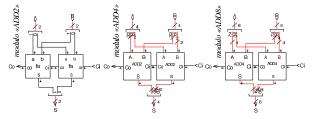

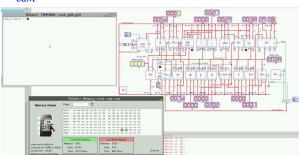

Figura u109.1. Il bus della CPU con l'aggiunta dell'unità ALU.

Figura u109.2. La struttura della ALU: si deve fare attenzione a non confondere le linee da un solo bit (di colore nero), rispetto a quelle che ne raccolgono in ranghi maggiori (di colore rosso).

841

«a2» 2013.11.11 --- Copyright © Daniele Giacomini -- appunti2@gmail.com http://informaticalib

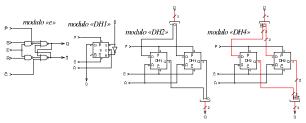

Figura u109.3. Modulo shift che si occupa di gestire gli scorrimenti e le rotazioni dei bit.

Figura u109.4. Modulo sh, contenuto nel modulo shift, per lo scorrimento dei bit.

Figura u109.5. Modulo as della ALU che ha il compito di sommare o sottrarre gli ingressi.

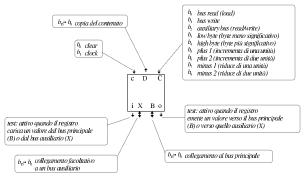

Nel codice che descrive i campi del bus di controllo, si aggiungono quelli seguenti, i quali servono specificatamente a gestire la ALU. Si può osservare che la ALU ha il controllo di scrittura nel bus, ma non quello di lettura, dato che dal bus non riceve dati, e richiede il controllo della funzione che vi si vuole svolgere :

```

field alu_f[22:19]={

not_a=0,

a_and_b=1,

a_or_b=2,

a_xor_b=3,

logic_shift_left=4,

logic_shift_right=5,

arith_shift_left=6,

```

```

arith_shift_right=7,

rotate_left=8,

rotate_right=9,

rotate_carry_left=10,

rotate_carry_right=11,

a_plus_b_carry=12,

a_minus_b_borrow=13,

a_plus_b=14,

a_minus_b=15

};

field alu_bw[23];  // ALU --> bus

field fl_ar[24];  // FL <-- ALU</pre>

```

Tra i campi del bus di controllo si vede anche  $fl_ar$  che per ora può essere ignorato: viene chiarito il suo utilizzo quando nella prossima versione della CPU dimostrativa si aggiunge il registro FL. Attualmente, nel microcodice vi si fa già riferimento, perché le microistruzioni prese ora in considerazione, in un secondo momento devono avere a che fare con tale registro.

Nell'elenco dei codici operativi si aggiungono istruzioni nuove e lo stesso poi nella descrizione del microcodice:

```

op not {

map not : 32;

// A = NOT A

+0[7:0]=32;

operands op_0;

};

op and {

map and : 33;

// A = A AND B

+0[7:0]=33;

operands op_0;

};

op or {

map or : 34;

// A = A OR B

+0[7:0]=34;

operands op_0;

op xor {

map xor : 35;

// A = A OR B

+0[7:0]=35;

operands op_0;

op 1shl {

map lshl : 36;

//A = A << 1

+0[7:0]=36;

operands op_0;

op 1shr {

map lshr : 37;

// A = A >> 1

+0[7:0]=37;

operands op_0;

op ashl {

map ashl : 38;

+0[7:0]=38;

operands op_0;

op ashr {

map ashr : 39;

+0[7:0]=39;

operands op_0;

op rotl {

map rotl : 40;

// A = A rotate left

+0[7:0]=40;

operands op_0;

op rotr {

map rotr : 41;

// A = A rotate right

+0[7:0]=41;

operands op_0;

op add {

map add : 46;

//A = A + B

+0[7:0]=46;

operands op 0;

};

op sub {

map sub : 47;

//A = A - B

+0[7:0]=47;

```

operands op\_0;

};

```

begin microcode @ 0

a_br alu_f=not_a alu_bw fl_ar;

// A <-- NOT A

ctrl_start ctrl_load;

// CNT <-- 0

and:

a_br alu_f=a_and_b alu_bw fl_ar;

// A <-- A AND B

ctrl_start ctrl_load;

// CNT <-- 0

or:

// A <-- A OR B

a br alu f=a or b alu bw fl ar;

ctrl_start ctrl_load;

// CNT <-- 0

//

xor:

a_br alu_f=a_xor_b alu_bw fl_ar;

// A <-- A XOR B

ctrl_start ctrl_load;

// CNT <-- 0

lshl:

a_br alu_f=logic_shift_left alu_bw fl_ar; // A <-- A << 1

ctrl_start ctrl_load;

// CNT <-- 0

lshr:

a_br alu_f=logic_shift_right alu_bw fl_ar; // A <-- A >> 1

ctrl_start ctrl_load;

// CNT <-- 0

ashl:

a_br alu_f=arith_shift_left alu_bw fl_ar; // A <-- A*2

ctrl start ctrl load;

// CNT <-- 0

ashr:

a_br alu_f=arith_shift_right alu_bw fl_ar; // A <-- A/2

// CNT <-- 0

ctrl_start ctrl_load;

rotl:

a_br alu_f=rotate_left alu_bw fl_ar; // A <-- A rot. left

ctrl_start ctrl_load;

// CNT <-- 0

a_br alu_f=rotate_right alu_bw fl_ar; // A <-- A rot. right

ctrl_start ctrl_load;

// CNT <-- 0

add:

a_br alu_f=a_plus_b alu_bw fl_ar; // A <-- A + B

// CNT <-- 0

ctrl_start ctrl_load;

sub:

a_br alu_f=a_minus_b alu_bw fl_ar;

// A <-- A - B

ctrl_start ctrl_load;

// CNT <-- 0

```

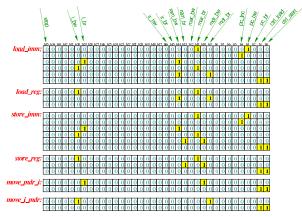

Figura u109.9. Corrispondenza con il contenuto della memoria che rappresenta il microcodice (la coppia *m1* e *m2* dell'unità di controllo).

Tabella u109.10. Elenco delle macroistruzioni aggiunte in questa versione della CPU dimostrativa. Nella descrizione sintetica delle operazioni si usa la notazione del linguaggio C.

| Sintassi | Descrizione Descrizione                             |

|----------|-----------------------------------------------------|

|          | $A = \sim A$                                        |

| not      | Complemento a uno del contenuto di A.               |

|          | A = A & B                                           |

| and      | Si assegna ad A il risultato di A AND B,            |

|          | bit per bit.                                        |

|          | $A = A \mid B$                                      |

| or       | Si assegna ad $A$ il risultato di $A$ OR $B$ , bit  |

| 01       | per bit.                                            |

|          | $A = A \wedge B$                                    |

| xor      |                                                     |

| AUI      | Si assegna ad $A$ il risultato di $A$ XOR $B$ ,     |

|          | bit per bit. $A = A << 1$                           |

|          |                                                     |

| lshl     | Si assegna ad A il risultato dello scor-            |

|          | rimento logico a sinistra dei bit di                |

|          | $A = A \gg 1$                                       |

| lshr     |                                                     |

| Ishr     | Si assegna ad A il risultato dello scorri-          |

|          | mento logico a destra dei bit di $A$ . $A = A << 1$ |

|          |                                                     |

| ashl     | Si assegna ad A il risultato dello scorri-          |

|          | mento aritmetico a sinistra dei bit di $m{A}$ (in   |

|          | pratica è identico a lshl).                         |

|          | $A = A \gg 1$                                       |

| ashr     | Si assegna ad A il risultato dello scor-            |

|          | rimento aritmetico a destra dei bit di              |

|          | A.                                                  |

| rotl     | Si assegna ad A il risultato della rotazione        |

|          | a sinistra dei bit di A.                            |

| rotr     | Si assegna ad A il risultato della rotazione        |

|          | a destra dei bit di $A$ .<br>A = A + B              |

|          | 11 11 12                                            |

| add      | Si assegna ad A il risultato della somma            |

|          | di $A \in B$ , senza tenere conto del riporto       |

|          | precedente.                                         |

| Sintassi | Descrizione                                   |

|----------|-----------------------------------------------|

|          | A = A - B                                     |

| sub      | Si assegna ad A il risultato della sottra-    |

| Sub      | zione di $A$ e $B$ , senza tenere conto della |

|          | richiesta di prestito precedente.             |

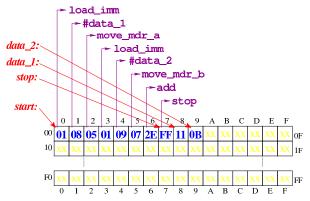

Nelle sezioni successive, vengono proposti diversi esempi, nei quali si sperimentano tutte le istruzioni nuove introdotte.

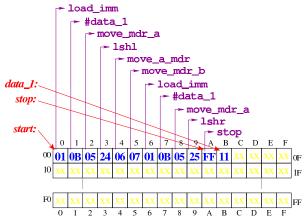

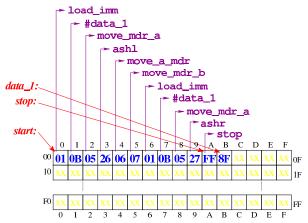

#### Istruzione «not»

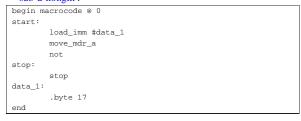

Listato u 109.11. Macrocodice per sperimentare l'istruzione  $\mathtt{not}$ : si carica un valore dalla memoria, lo si copia nel registro A, si calcola il complemento a uno e il risultato va ad aggiornare il registro A. Il file completo che descrive le memorie per Tkgate dovrebbe essere disponibile presso *allegati/circuiti-logici/scpu-sub-d-not.gm*.

Figura u109.12. Contenuto della memoria RAM. Le celle indicate con «xx» hanno un valore indifferente.

Figura u109.13. Situazione conclusiva del bus dati, dopo l'esecuzione dell'istruzione not. Video: http://www.youtube.com/watch?v=x5Vnhd72vh728

### Istruzione «and»

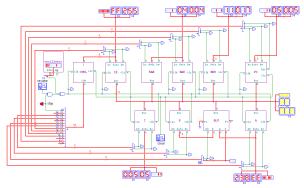

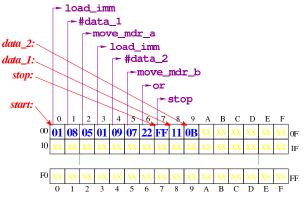

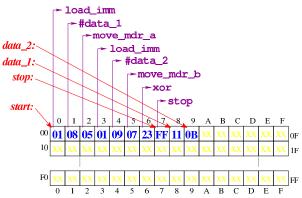

Listato u 109.14. Macrocodice per sperimentare l'istruzione and: si caricano dalla memoria i valori da assegnare ai registri  $A \in B$ , quindi si esegue un AND binario che va ad aggiornare il registro A. Il file completo che descrive le memorie per Tkgate dovrebbe essere disponibile presso allegati/circuiti-logici/scpu-sub-d-and. gm.

```

begin macrocode @ 0

```

```

start:

load_imm #data_1

move_mdr_a

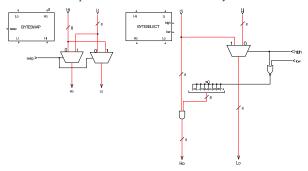

load_imm #data_2